-

-

Rapid IO

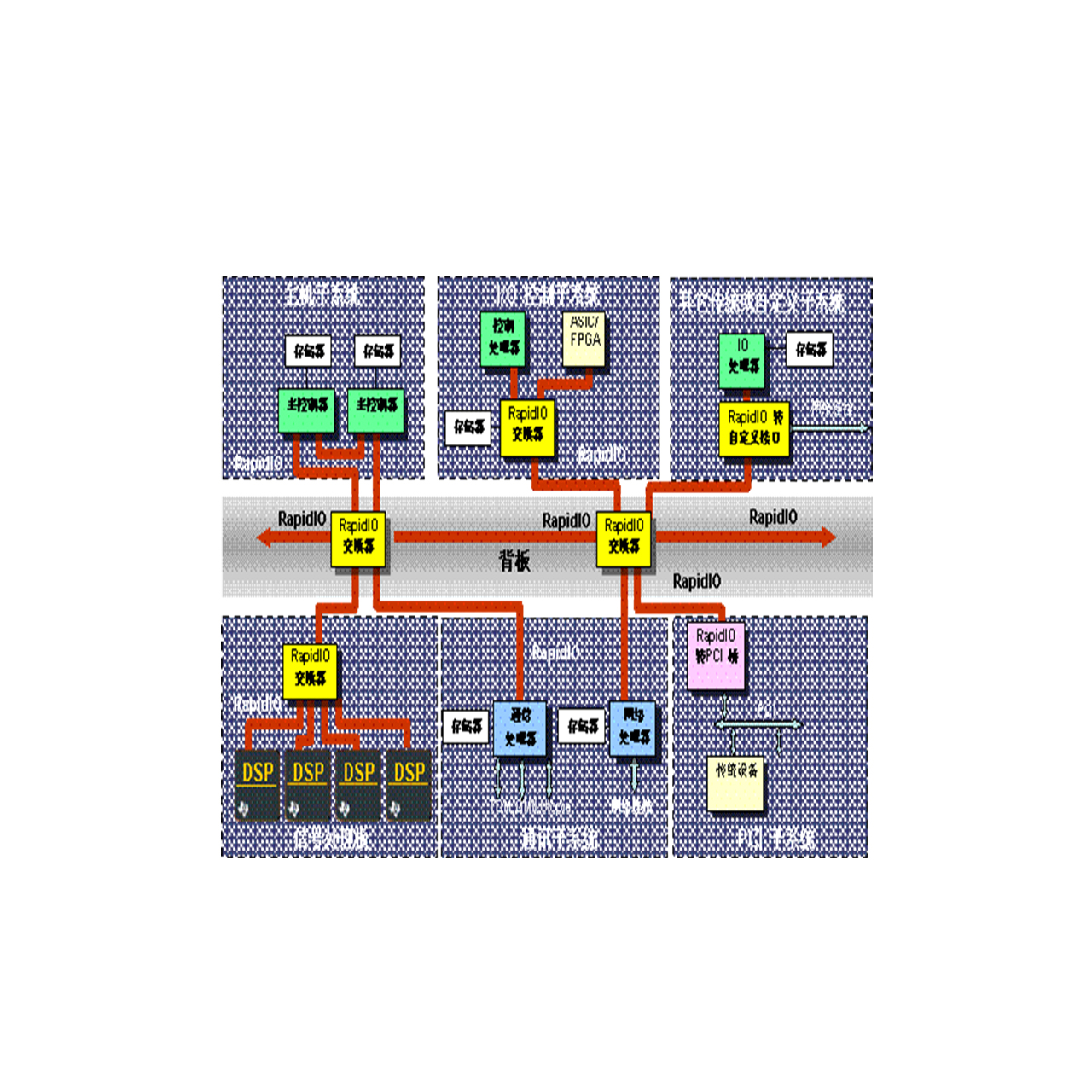

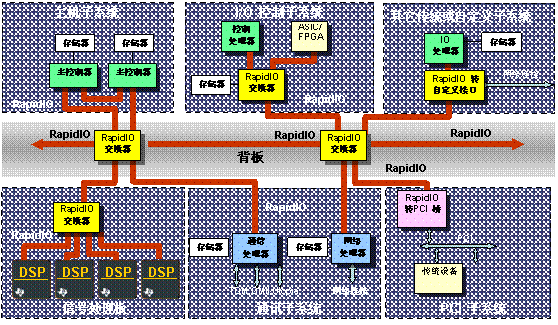

RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板(Backplane)连接”。目前,RapidIO总线信号经光电转换后,可实现机箱和机箱之间的高带宽、低延时的数据传输。RapidIO常用于数据中心、通信设备、无线基站、雷达、航空电子等领域。-

0.000.00

-

Rapid IO 是由 Motorola 和 Mercury 等公司率先倡导的一种高性能、 低引脚数、 基于数据包交换的互连体系结构,是为满足和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板(Backplane)连接”。目前,RapidIO总线信号经光电转换后,可实现机箱和机箱之间的高带宽、低延时的数据传输。RapidIO常用于数据中心、通信设备、无线基站、雷达、航空电子等领域。

在实际的嵌入式、测控系统搭建中,常需要Rapid IO仿真传输卡实现多个Rapid IO(SRIO)的光或电接口。创信航电子提供Rapid IO传输仿真卡、交换机和协议分析仪。Rapid IO传输仿真卡提供PCIe、PXIe、XMC、VPX、USB4.0、雷电3/4等总线接口的产品,支持1 ~ 48个SRIO光纤通道传输通道,模式支持×1、×2、×4,速率支持1.25Gbps、2.5Gbps、3.125Gbps、6.25Gbps,详情请见:Rapid IO传输仿真产品线。

RapidIO创建背景

针对嵌入式系统的需求以及传统互连方式的局限性,RapidIO标准按如下目标被制定:

Ø针对嵌入式系统机框内高速互连应用而设计。

Ø简化协议及流控机制,限制软件复杂度,使得纠错重传机制乃至整个协议栈易于用硬件实现。

Ø提高打包效率,减小传输时延。

Ø减少管脚,降低成本。

Ø简化交换芯片的实现,避免交换芯片中的包类型解析。

分层协议结构,支持多种传输模式,支持多种物理层技术,灵活且易于扩展。

图1 RapidIO在嵌入式系统中的应用

表1总结比较了的三种带宽能达到10Gbps的互连技术:以太网,PCI Express和串行RapidIO,从中可以看出串行RapidIO是最适合高性能嵌入式系统互连的技术。

表1 10G级互连技术比较

软件实现TCP/IP 协议栈的以太网 | 4x PCI Express | 4x SRIO | 备注 | |

软件开销 | 高 | 中 | 低 | SRIO 协议栈简单,一般都由硬件实现,软件开销很小 |

硬件纠错重传 | 不支持 | 支持 | 支持 | |

传输模式 | 消息 | DMA | DMA,消息 | |

拓扑结构 | 任意 | PCI树 | 任意 | SRIO支持直接点对点或通过交换器件实现的各种拓扑结构 |

直接点对点对等互连 | 支持 | 不支持 | 支持 | SRIO互连双方可对等的发起传输。 |

传输距离 | 长 | 中 | 中 | SRIO针对嵌入式设备内部互连,传输距离一般小于1米 |

数据包最大有效载荷长度 | 1500字节 | 4096字节 | 256字节 | 嵌入式通信系统对实时性要求高,SRIO小包传输可减少传输时延 |

打包效率 (以传输256字节数据为例) | 79% (TCP包) | 82% | 92~94% | 打包效率是有效载荷长度与总包长的比率。SRIO支持多种高效包格式。 |

串行RapidIO协议

串行RapidIO(Serial RapidIO,缩写为:SRIO)是物理层采用串行差分模拟信号传输的RapidIO标准。目前,通用的标准为SRIO 2.2,该标准支持的信号速度为1.25GHz、2.5GHz、3.125GHz、5GHz、6.25GHz。目前,几乎所有的嵌入式系统芯片及设备供应商都加入了RapidIO行业协会。

RapidIO协议结构及包格式

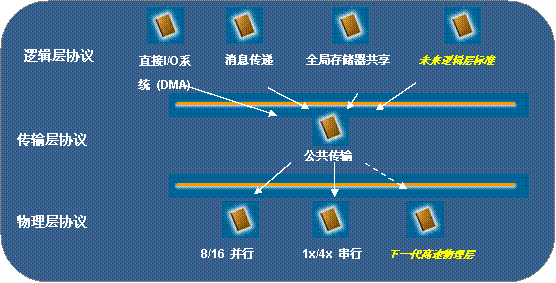

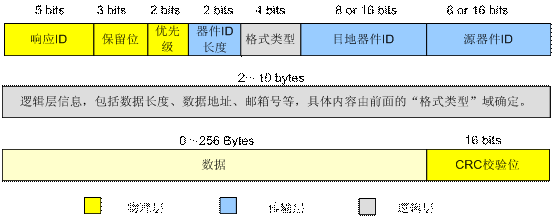

为了满足灵活性和可扩展性的要求,RapidIO协议分为三层:逻辑层、传输层和物理层。图2说明了RapidIO协议的分层结构。

RapidIO协议分层结构

逻辑层定义了操作协议; 传输层定义了包交换、路由和寻址机制;物理层定义了电气特性、链路控制和纠错重传等。

与以太网一样,RapidIO也是基于包交换的互连技术。如图3所示,RapidIO包由包头、可选的载荷数据和16bits CRC校验组成。包头的长度因为包类型不同可能是十几到二十几个字节。每包的载荷数据长度不超过256字节,这有利于减少传输时延,简化硬件实现。

RapidIO包格式

上述包格式定义兼顾了包效率及组包/解包的简单性。RapidIO交换器件仅需解析前后16bits,以及源/目地器件ID,这简化了交换器件的实现。

逻辑层协议

逻辑层定义了操作协议和相应的包格式。RapidIO支持的逻辑层业务主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息传递(Message Passing)。直接IO/DMA模式是最简单实用的传输方式,其前提是主设备知道被访问端的存储器映射。在这种模式下,主设备可以直接读写从设备的存储器。直接IO/DMA在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。从功能上讲,这一特点和德州仪器DSP的传统的主机接口(HPI, Host Port Interface)类似。但和HPI口相比,SRIO(Serial RapidIO)带宽大,管脚少,传输方式更灵活。

对上层应用来说,发起直接IO/DMA传输主要需提供以下参数:目地器件ID、数据长度、数据在目地器件存储器中的地址。

直接IO/DMA模式又可进一步分为以下几种传输格式:

ØNWRITE: 写操作,不要求接收端响应。

ØNWRITE_R: 带响应的NWRITE(NWRITE with Response),要求接收端响应。

ØSWRITE:流写(Stream Write),数据长度必须是8字节的整数倍,不要求接收端响应。

ØNREAD: 读操作。

ØSWRITE是最高效的传输格式;带响应的写操作或读操作效率则较低,一般只能达到不带响应的传输的效率的一半。

Ø消息传递(Message Passing)模式则类似于以太网的传输方式,它不要求主设备知道被访问设备的存储器状况。数据在被访问设备中的位置则由邮箱号(类似于以太网协议中的端口号)确定。从设备根据接收到的包的邮箱号把数据保存到对应的缓冲区,这一过程往往无法完全由硬件实现,而需要软件协助,所以会带来一些软件负担。对上层应用来说,发起消息传递主要需提供以下参数:目地器件ID、数据长度、邮箱号。

传输层协议

RapidIO是基于包交换的互连技术,传输层定义了包交换的路由和寻址机制。

RapidIO网络主要由两种器件,终端器件(End Point)和交换器件(Switch)组成。终端器件是数据包的源或目的地,不同的终端器件以器件ID来区分。RapidIO支持8 bits 或 16 bits器件ID,因此一个RapidIO网络最多可容纳256或65536个终端器件。与以太网类似,RapidIO也支持广播或组播,每个终端器件除了独有的器件ID外,还可配置广播或组播ID。交换器件根据包的目地器件ID进行包的转发,交换器件本身没有器件ID。RapidIO的互连拓扑结构非常灵活,除了通过交换器件外,两个终端器件也可直接互连。

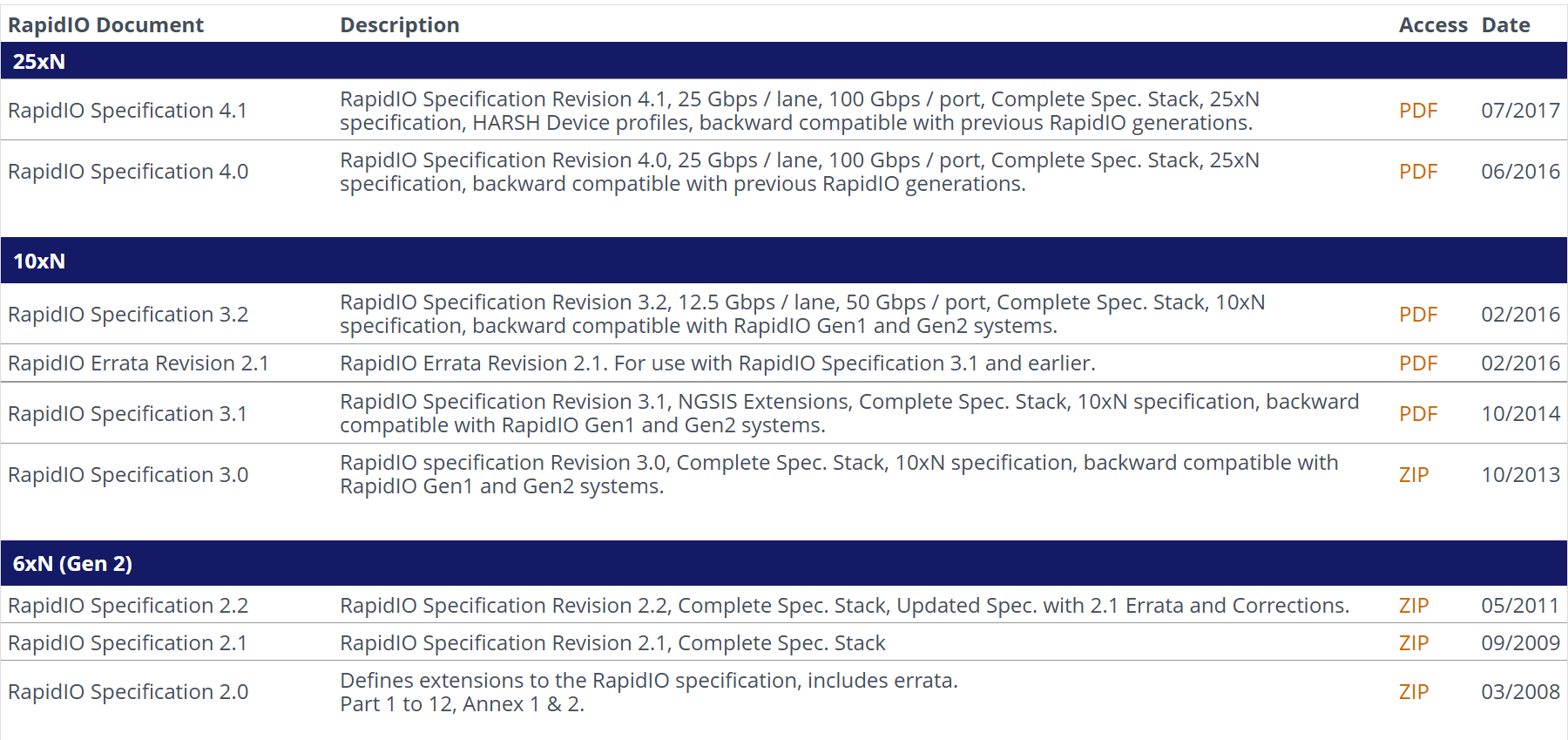

SRIO协议规范

深入了解 Rapid IO 互联特性,可到VITA官网(VITA - rapidio-specifications)下载RapidIO Interconnect Specification,最新版本是《RapidIO Specification 4.1》。

目前,国内嵌入式领域应用最广泛的版本是《RapidIO Specification 2.2》。

联系人:何先生

联系地址:江苏省无锡市滨湖区

建筑西路777号A3-1801

联系邮箱:henry@ccateco.com

咨询时间:周一~周五(9:00-18:00)

联系方式:15000972046

全国咨询热线: